# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### DESCRIPTION

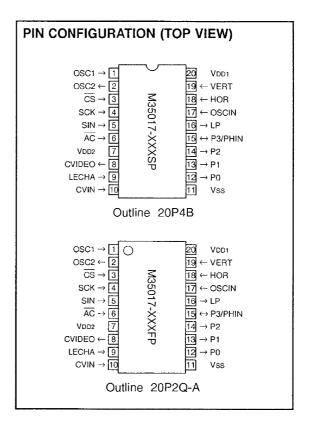

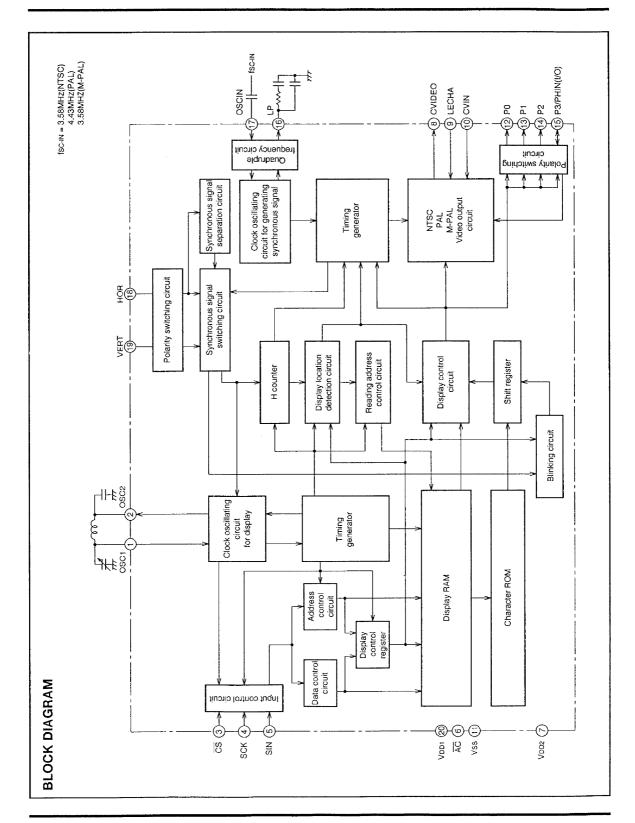

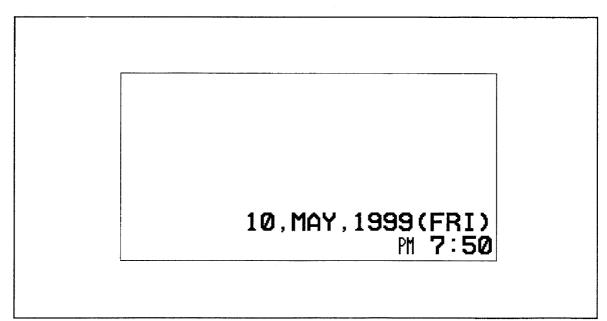

The M35017-XXXSP/FP is a TV screen display control IC which can be used to display information such as program schedules, the data and messages on the TV screen.

It uses a silicon gate CMOS process and M35017-XXXSP is housed in a 20-pin shrink DIP package, M35017-XXXFP is housed in a 20-pin shrink SOP package.

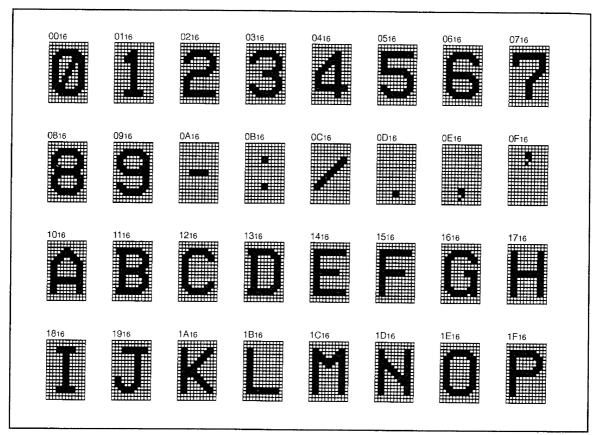

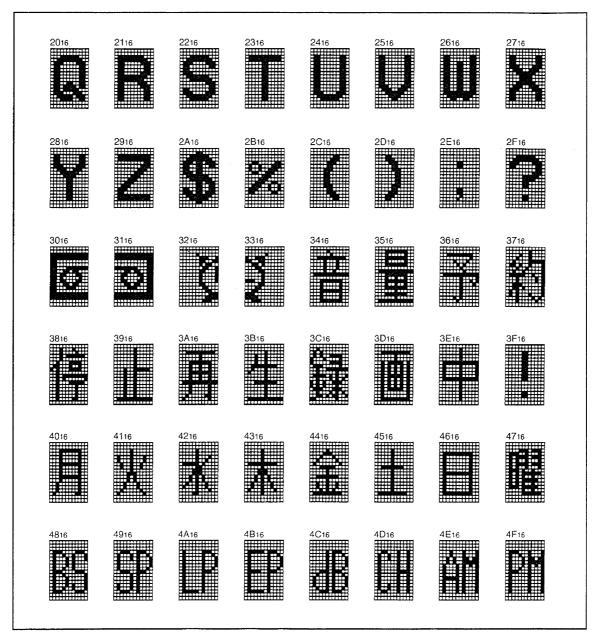

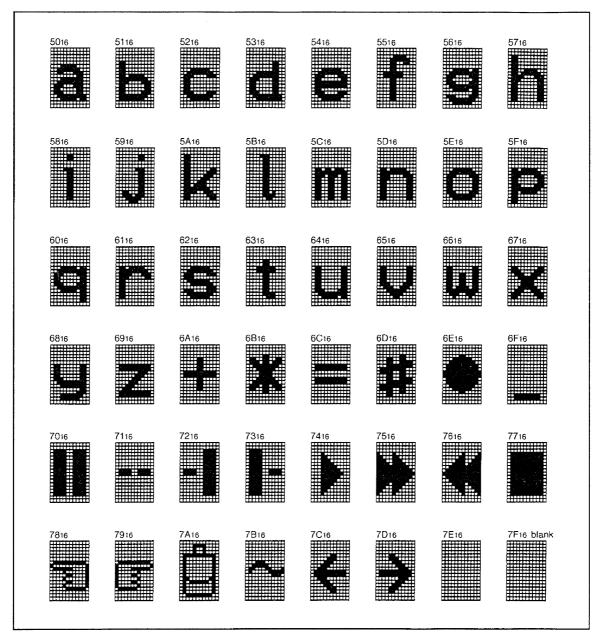

For M35017-001SP/FP that is a standard ROM version of M35017-XXXSP/FP respectively, the character pattern is also mentioned.

#### **FEATURES**

| LATORES                                                     |

|-------------------------------------------------------------|

| Screen composition                                          |

| Number of characters displayed                              |

| Character composition                                       |

| Characters available 128 characters                         |

| • Character sizes available 4 (horizontal) X 4 (vertical)   |

| Display locations available                                 |

| Horizontal direction                                        |

| Vertical direction                                          |

| Blinking Character units                                    |

| Cycle: approximately 1 second, or approximately 0.5 seconds |

| Duty : 25%, 50%, or 75%                                     |

| Data input                                                  |

| Coloring                                                    |

| Background coloring (composite video signal)                |

| Blanking                                                    |

|                                                             |

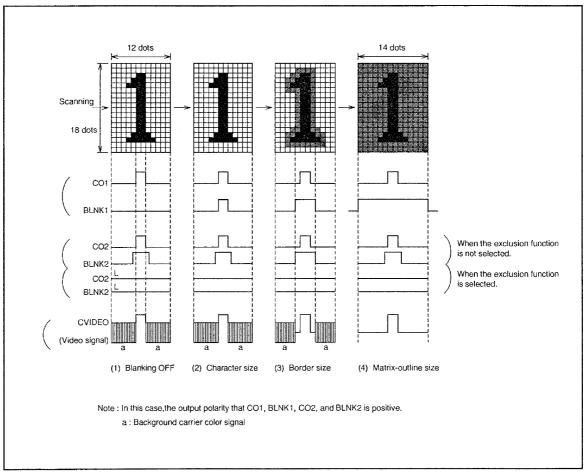

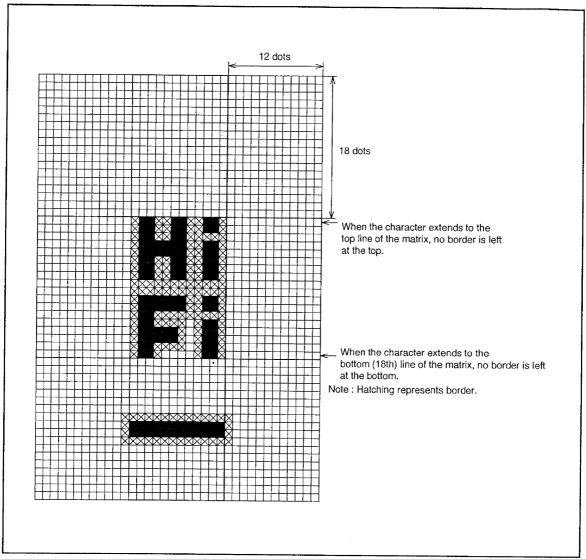

Total blanking (14  $\times$  18 dots)

Border size blanking

Character size blanking

Synchronization signal

Composite synchronization signal

Composite synchronization signal generation (PAL, NTSC, M-PAL)

- 4 output ports (2 digital lines)

- Oscillation stop function

Be possible to stop the oscillation for display

- Built-in the oscillation for synchronized signal generation

- Reversed character display function

- Be possible to background coloring in superimpose (NTSC, PAL, M-PAL)

- Built-in polarity switching function at horizontal synchronized signal or vertical synchronized signal is input.

## **APPLICATION**

TV, VCR, Camcorder

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## PIN DESCRIPTION

| of external oscillator circuit Output tal position of the display on the TV screen and the width of the characters.  Output tal position of the display on the TV screen and the width of the characters.  Chip select input Input This is the chip select pin, and when serial data transmission is being carried out, it goes to "L".  SCK Serial clock input Input When CS pin is "L", SIN serial data is taken in when SCK rises. Hysteresis input. Built-in pull-up resistor.  SIN Serial data input Input When "This is the pin for serial input of data and addresses for the display control register and the display data memory. Hysteresis input. Includes built-in pull-up resistor.  Auto-clear input Input When "L", this pin resets the internal IC circuit. Hysteresis input. Includes built-in pull-up resistor.  Please connect to +5 V with the analog circuit power pin.  CVIDEO Composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.  Port Po output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  Port Po output Output This pin can be toggled between port pin output and BLNK2 (ch | Pin<br>Number | Symbol  | Pin name                                   | Input/<br>Output | Function                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|--------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 OSC2 circuit Output tal postlor of the display on the TV screen and the width of the characters.  3 SS Chip select input Input Input Hysteresis input. Includes built-in pull-up resistor.  4 SCK Serial clock input Input When SS pin is "L", SIN serial data is taken in when SCK rises. Hysteresis input. Built-in pull-up resistor is included.  5 SIN Serial data input Input This is the pin for serial input of data and addresses for the display control register and the display data and addresses for the display control register and the display control register and the display data and addresses for the display control register and the display data data is taken in when SCK rises. Hysteresis input. Built-in pull-up resistor.  This is the output pin for external IC dirout. Hysteresis input. Includes built-in pull-up resistor.  This is the input pin for external IC dirout. Hysteresis input. Includes built-in pull-up resistor.  This is the output pin of external IC dirout. Hysteresis  | 1             | OSC1    |                                            | Input            | There are the pins for attaching an external display oscillator circuit. The standard oscillation frequency is approximately 7 MHz. This oscillation frequency determines the horizon-                     |

| Hysteresis input. Includes built-in pull-up resistor.  Kock Serial clock input Input When CS pin is "L", SIN serial data is taken in when SCK rises. Hysteresis input. Built-in pull-up resistor is included.  SIN Serial data input Input This is the pin for serial input of data and addresses for the display control register and the display data memory. Hysteresis input. Includes built-in pull-up resistor.  Nobel Power pin — Please connect to +5 V with the analog circuit power pin.  Please connect to +5 V with the analog circuit power pin.  CVIDEO Composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals from CVIN.  Composite video signal Input This is the input pin for composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals in a linput and input output and composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.  Port P1 output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  Port P2 output Output This pin can be toggled between port pin output and CO1 (character) signal output. This pin can be toggled between port pin output and CO2 (character) signal output. This pin can be toggled between port pin output and CO2 (character) signal output. This pin can be toggled between port pin output and CO2 (character) signal output. Superingosed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  Port P2 output This pin connects filter circuit.  This pin can be toggled between port pin outp | 2             | OSC2    |                                            | Output           | tal position of the display on the TV screen and the width of the characters.                                                                                                                              |

| pull-up resistor is included.  SIN Serial data input Input This is the pin for serial input of data and addresses for the display control register and the display data memory. Hysteresis input. Includes built-in pull-up resistor.  Vidoz Power pin – Please connect to +5 V with the analog circuit, Hysteresis input. Includes built-in pull-up resistor.  CVIDEO Composite video signals and output Insurering the authorization signal input Insurering the external composite video signals. In outputs 2Vp-p composite video signals in superimpose mode, character output etc. is superimposed on the external composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. In the composite video signals. In the composite video signals. In the composite video signals. Input is is the input pin which determines the "white" character luminance level in the composite video signals.  CVIN Composite video signal.  This is the input pin which determines the "white" character luminance level in the composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals. In Search of the composite video signals.  This is the input pin for external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.  Port PO output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  Port P1 output for composite video signals. Input This pin inputs the horizontal synchronization signal. Hysteresis input.                                                                                                                 | 3             | CS      | Chip select input                          | Input            | This is the chip select pin, and when serial data transmission is being carried out, it goes to "L". Hysteresis input. Includes built-in pull-up resistor.                                                 |

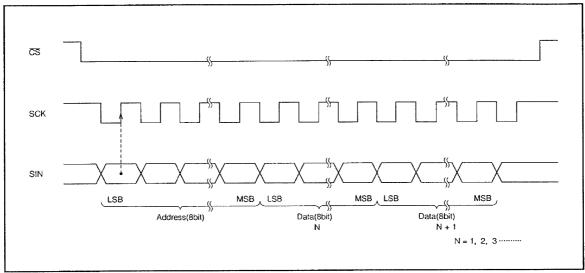

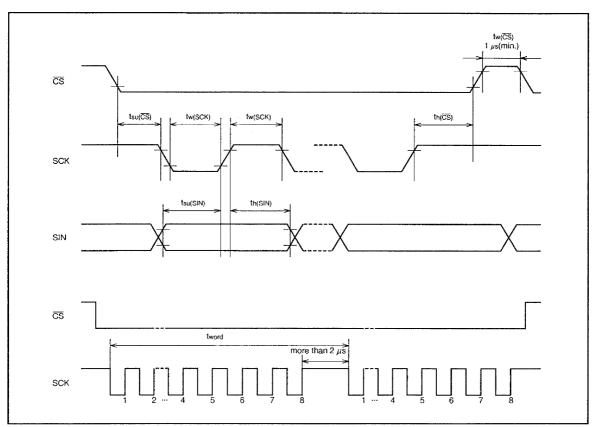

| display data memory. Hysteresis input. Includes built-in pull-up resistor.  Auto-clear input Input When "L", this pin resets the internal IC circuit. Hysteresis input. Includes built-in pull-up resistor.  Please connect to +5 V with the analog circuit power pin.  CVIDEO Composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. It outputs 2Vp-p composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals from CVIN.  Composite video signal.  Input This is the input pin which determines the "white" character luminance level in the composite video signals. In superimpose mode, character output etc. is superimpose mode, character output etc. in superimpose mode, character output etc. in superimposed on the external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.  Please connect to GND using circuit earthing pin.  This pin can be toggled between port pin output and BLNK1 (character background) signal output.  Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  PayPHIN Port P3 output I/O This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL at NTSC, 4.43 MHz at PAL and 3.5 | 4             | SCK     | Serial clock input                         | Input            | When $\overline{\text{CS}}$ pin is "L", SIN serial data is taken in when SCK rises. Hysteresis input. Built-in pull-up resistor is included.                                                               |

| 7 VDD2 Power pin — Please connect to +5 V with the analog circuit power pin.  8 CVIDEO Composite video signals output this is the output pin for composite video signals. It outputs 2VP-p composite video signals in superimpose mode, character output etc. is superimposed on the external composite video signals from CVIN.  9 LECHA Character level input Input input in this is the input pin which determines the "white" character luminance level in the composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.  10 CVIN Composite video signal.  11 Vss Earthing pin — Please connect to GND using circuit earthing pin.  12 P0 Port P0 output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  13 P1 Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  14 P2 Port P2 output Output This pin can be toggled between port pin output and BLNK2 (character background) signal output.  15 P3/PHIN Port P3 output WO This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  16 LP Filter connection pin Output This pin connects filter circuit.  17 P3/PHIN Port P3 output In of oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  18 HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                               | 5             | SIN     | Serial data input                          | Input            | This is the pin for serial input of data and addresses for the display control register and the display data memory. Hysteresis input. Includes built-in pull-up resistor.                                 |

| Record Composite video signals. Output In is is the output pin for composite video signals. It outputs 2Vp-p composite video signals in superimpose mode, character output etc. is superimposed on the external composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. In put in the input pin which determines the "white" character luminance level in the composite video signals. In superimpose mode, character output etc. is superimposed on the external composite video signals. In superimpose mode, character output etc. In superimpose mode etc. In superimpose mode output etc. In superimpose mode etc. In superimpose mode etc. In superimpose mode etc. In superimpose mode output etc. In superimpose mode etc. In superimpose mode etc. In superimpose mode etc. In superimpose mode etc. In superimpose on these external composite video signals. In superimpose mode etc. In superimpose mode etc. In superimpose do these external composite video signals. In superimpose do these external composite video signals. In superimpose do these external composite video signals. In superimpose do these external composite video signal output.  In spirit put etc. is superimpose do these external composite video signals. In superimpose do these external composi | 6             | ĀC      | Auto-clear input                           | Input            | When "L", this pin resets the internal IC circuit. Hysteresis input. Includes built-in pull-up resistor.                                                                                                   |

| lin superimpose mode, character output etc. is superimposed on the external composite video signals from CVIN.    Possible video signal input   This is the input pin which determines the "white" character luminance level in the composite video signal.    CVIN   Composite video signal   Input   This is the input pin for external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals. In superimpose mode, character national input   This pin can be toggled between port pin output and BLNK1 (character background) signal output.    Potential Po | 7             | VDD2    | Power pin                                  | -                | Please connect to +5 V with the analog circuit power pin.                                                                                                                                                  |

| ite video signal.  CVIN Composite video signal.  This is the input pin for external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.  Poscarting pin — Please connect to GND using circuit earthing pin.  Port P0 output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  Port P2 output This pin can be toggled between port pin output and BLNK2 (character background) signal output.  Port P3 output ViO This pin can be toggled between port pin output and CO2 (character) signal output.  Port P3 output ViO This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  CSCIN fiscinput pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  This pin inputs the horizontal synchronization signal. Hysteresis input.  This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8             | CVIDEO  |                                            | Output           | In superimpose mode, character output etc. is superimposed on the external composite                                                                                                                       |

| nal input output etc. is superimposed on these external composite video signals.  11 Vss Earthing pin — Please connect to GND using circuit earthing pin.  12 P0 Port P0 output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  13 P1 Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  14 P2 Port P2 output Output This pin can be toggled between port pin output and BLNK2 (character background) signal output.  15 P3/PHIN Port P3 output I/O Iii pin can be toggled between port pin output and CO2 (character background) signal output.  16 LP Filter connection pin Output This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  17 OSCIN fsc input pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  18 HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.  19 VERT Vertical synchronization input Input This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9             | LECHA   | Character level input                      | Input            | This is the input pin which determines the "white" character luminance level in the composite video signal.                                                                                                |

| Port P0 output Output This pin can be toggled between port pin output and BLNK1 (character background) signal output.  Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  P2 Port P2 output Output This pin can be toggled between port pin output and BLNK2 (character background) signal output.  P3/PHIN Port P3 output I/O This pin can be toggled between port pin output and BLNK2 (character background) signal output.  P3/PHIN Port P3 output I/O This pin can be toggled between port pin output and CO2 (character) signal output. Super-imposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  CSCIN fsc input pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.  This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10            | CVIN    |                                            | Input            | This is the input pin for external composite video signals. In superimpose mode, character output etc. is superimposed on these external composite video signals.                                          |

| output.  Port P1 output Output This pin can be toggled between port pin output and CO1 (character) signal output.  P2 Port P2 output Output This pin can be toggled between port pin output and BLNK2 (character background) signal output.  P3/PHIN Port P3 output I/O This pin can be toggled between port pin output and CO2 (character background) signal output.  P3/PHIN Port P3 output I/O This pin can be toggled between port pin output and CO2 (character) signal output. Super-imposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  CSCIN fsc input pin of oscillation circuit for generating the synchronization signal ton circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.  This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11            | Vss     | Earthing pin                               | -                | Please connect to GND using circuit earthing pin.                                                                                                                                                          |

| P2 Port P2 output Output This pin can be toggled between port pin output and BLNK2 (character background) signal output.  P3/PHIN Port P3 output I/O This pin can be toggled between port pin output and CO2 (character) signal output. Super-imposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  LP Filter connection pin Output This pin connects filter circuit.  OSCIN fsc input pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.  This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12            | P0      | Port P0 output                             | Output           | This pin can be toggled between port pin output and BLNK1 (character background) signal output.                                                                                                            |

| output.  P3/PHIN Port P3 output  I/O This pin can be toggled between port pin output and CO2 (character) signal output. Super-imposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  LP Filter connection pin Output This pin connects filter circuit.  OSCIN fsc input pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.  This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13            | P1      | Port P1 output                             | Output           | This pin can be toggled between port pin output and CO1 (character) signal output.                                                                                                                         |

| imposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal.  16 LP Filter connection pin Output This pin connects filter circuit.  17 OSCIN fsc input pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  18 HOR Horizontal synchronization signal input This pin inputs the horizontal synchronization signal. Hysteresis input.  19 VERT Vertical synchronization signal input This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14            | P2      | Port P2 output                             | Output           | This pin can be toggled between port pin output and BLNK2 (character background) signal output.                                                                                                            |

| OSCIN fsc input pin of oscillation circuit for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  HOR Horizontal synchronization signal input  WERT Vertical synchronization signal input  This pin inputs the horizontal synchronization signal. Hysteresis input.  This pin inputs the horizontal synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15            | P3/PHIN | Port P3 output                             | I/O              | This pin can be toggled between port pin output and CO2 (character) signal output. Superimposed colors on the PAL and M-PAL systems are controlled by the input terminal of the color burst select signal. |

| tion circuit for generating the synchronization signal  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.  (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16            | LP      | Filter connection pin                      | Output           | This pin connects filter circuit.                                                                                                                                                                          |

| nization signal input  VERT Vertical synchronization signal input  This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17            | OSCIN   | tion circuit for generating the synchroni- | Input            | This is the subcarrier frequency (fsc) input pin for generating the synchronization signal (Note). This pin inputs the oscillation of 3.58 MHz at NTSC, 4.43 MHz at PAL and 3.58 MHz at M-PAL.             |

| 19 zation signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18            | HOR     |                                            | Input            | This pin inputs the horizontal synchronization signal. Hysteresis input.                                                                                                                                   |

| 20 VDD1 Power pin – Please connect +5 V with the digital circuit power pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19            | VERT    |                                            | Input            | This pin inputs the vertical synchronization signal. Hysteresis input.                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20            | VDD1    | Power pin                                  | -                | Please connect +5 V with the digital circuit power pin.                                                                                                                                                    |

Note: Refer to Note for other (Note for fsc signal input).

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## **MEMORY CONSTITUTION**

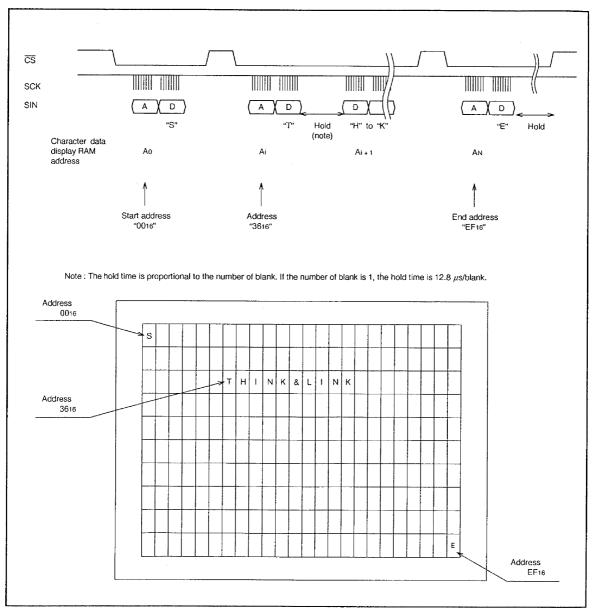

Address 0016 to EF16 are assigned to the display RAM, address F016 to F816 are assigned to the display control registers. The internal circuit is reset and all display control registers (address F016 to F816) are set to "0" and RAM is erased when the  $\overline{AC}$  pin level is "L".

| Bit<br>Address | DA7           | DA6       | DA5       | DA4       | DA3           | DA2        | DA1        | DA0        | Remarks                                   |

|----------------|---------------|-----------|-----------|-----------|---------------|------------|------------|------------|-------------------------------------------|

| 0016           | EXP           | C6        | C5        | C4        | Сз            | C2         | C1         | Co         |                                           |

|                | Expansion bit |           |           | (         | Character cod | e          |            |            | Display RAM                               |

| EF16           | EXP           | C6        | C5        | C4        | C3            | C2         | C1         | Co         |                                           |

| F016           | PTD<br>3      | PTD<br>2  | PTD<br>1  | PTD<br>0  | PTC<br>3      | PTC<br>2   | PTC<br>1   | PTC<br>0   | Port output specify                       |

| F116           | PLTV          | PLTH      | HP<br>5   | HP<br>4   | HP<br>3       | HP<br>2    | HP<br>1    | HP<br>0    | Horizontal display start position specify |

| F216           | INT/NON       | SEPV      | VP<br>5   | VP<br>4   | VP<br>3       | VP<br>2    | VP<br>1    | VP<br>0    | Vertical display start position specify   |

| F316           | VSZ<br>21     | VSZ<br>20 | VSZ<br>11 | VSZ<br>10 | HSZ<br>21     | HSZ<br>20  | HSZ<br>11  | HSZ<br>10  | Character size specify                    |

| F416           | DSP<br>7      | DSP<br>6  | DSP<br>5  | DSP<br>4  | DSP<br>3      | DSP<br>2   | DSP<br>1   | DSP<br>0   | Display mode specify                      |

| F516           | N/P           | TEST<br>2 | TEST<br>1 | TEST<br>0 | EXP<br>1      | EXP<br>0   | DSP<br>9   | DSP<br>8   | Expansion                                 |

| F616           | EQP           | PAL<br>H  | MPAL      | ALL<br>24 | SCOR          | BLINK<br>2 | BLINK<br>1 | BLINK<br>0 | Blinking specify and so on                |

| F716           | BLKHF         | BB        | BG        | BR        | LEVEL<br>0    | PHASE<br>2 | PHASE<br>1 | PHASE<br>0 | Raster color specify                      |

| F816           | DSP<br>ON     | CONT7F    | STOP<br>1 | TESTA     | RAM<br>ERS    | EΧ         | BLK<br>1   | BLK<br>0   | Control display                           |

Fig. 1 Memory constitution

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### **SCREEN CONSTITUTION**

The screen lines and rows are determined from each address of the display RAM. The screen constitution is shown in Figure 2.

| Row<br>Line | 1    | 2    | 3    | 4    | 5    | 6    | 7     | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   | 17   | 18   | 19   | 20   | 21   | 22   | 23   | 24   |

|-------------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 1           | 0016 | 0116 | 0216 | 0316 | 0416 | 0516 | 0616  | 0716 | 0816 | 0916 | 0A16 | 0B16 | 0C16 | 0B16 | 0E16 | 0F16 | 1016 | 1116 | 1216 | 1316 | 1416 | 1516 | 1616 | 1716 |

| 2           | 1816 | 1916 | 1A16 | 1B16 | 1C16 | 1D16 | 1E16  | 1F16 | 2016 | 2116 | 2216 | 2316 | 2416 | 2516 | 2616 | 2716 | 2816 | 2916 | 2A16 | 2B16 | 2C16 | 2D16 | 2E16 | 2F16 |

| 3           | 3016 | 3116 | 3216 | 3316 | 3416 | 3516 | 3616  | 3716 | 3816 | 3916 | 3A16 | 3B16 | 3C16 | 3D16 | 3E16 | 3F16 | 4016 | 4116 | 4216 | 4316 | 4416 | 4516 | 4616 | 4716 |

| 4           | 4816 | 4916 | 4A16 | 4B16 | 4C16 | 4D16 | 4E16  | 4F16 | 5016 | 5116 | 5216 | 5316 | 5416 | 5516 | 5616 | 5716 | 5816 | 5916 | 5A16 | 5B16 | 5C16 | 5D16 | 5E16 | 5F16 |

| 5           | 6016 | 6116 | 6216 | 6316 | 6416 | 6516 | 6616  | 6716 | 6816 | 6916 | 6A16 | 6B16 | 6C16 | 6D16 | 6E16 | 6F16 | 7016 | 7116 | 7216 | 7316 | 7416 | 7516 | 7616 | 7716 |

| 6           | 7816 | 7916 | 7A16 | 7B16 | 7C16 | 7D16 | 7E16  | 7F16 | 8016 | 8116 | 8216 | 8316 | 8416 | 8516 | 8616 | 8716 | 8816 | 8916 | 8A16 | 8B16 | 8C16 | 8D16 | 8E16 | 8F16 |

| 7           | 9016 | 9116 | 9216 | 9316 | 9416 | 9516 | 9616  | 9716 | 9816 | 9916 | 9A16 | 9B16 | 9C16 | 9D16 | 9E16 | 9F16 | A016 | A116 | A216 | A316 | A416 | A516 | A616 | A716 |

| 8           | A816 | A916 | AA16 | AB16 | AC16 | AD16 | AE16  | AF16 | B016 | B116 | B216 | B316 | B416 | B516 | B616 | B716 | B816 | B916 | BA16 | BB16 | BC16 | BD16 | BE16 | BF16 |

| 9           | C016 | C116 | C216 | C316 | C416 | C516 | C616  | C716 | C816 | C916 | CA16 | CB16 | CC16 | CD16 | CE16 | CF16 | D016 | D116 | D216 | D316 | D416 | D516 | D616 | D716 |

| 10          | D816 | D916 | DA16 | DB16 | DC16 | DD16 | DE 16 | DF16 | E016 | E116 | E216 | E316 | E416 | E516 | E616 | E716 | E816 | E916 | EA16 | EB16 | EC16 | ED16 | EE16 | EF16 |

The hexadecimal numbers in the boxes show the display RAM address.

Fig. 2 Screen constitution

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## **REGISTERS DESCRIPTION**

(1) Address F016

| DA       | Register  |        | Contents            | Dd                  |  |  |  |

|----------|-----------|--------|---------------------|---------------------|--|--|--|

| DA       | riegistei | Status | Function            | Remarks             |  |  |  |

| 0        | PTC0      | 0      | P0 output (port P0) |                     |  |  |  |

| U        | PICO      | 1      | BLNK1 output        |                     |  |  |  |

| 1        | PTC1      | 0      | P1 output (port P1) |                     |  |  |  |

| 1        | PICI      | 1      | CO1 output          |                     |  |  |  |

| 2        | PTC2      | 0      | P2 output (port P2) | Port output control |  |  |  |

|          | P102      | 1      | BLNK2 output        |                     |  |  |  |

| 3        | PTC3      | 0      | P3 output (port P3) |                     |  |  |  |

|          | FICS      | 1      | CO2 output          |                     |  |  |  |

| 4        | PTD0      | 0      | P0 output "L"       |                     |  |  |  |

| <b>-</b> | 1100      | 1      | P0 output "H"       |                     |  |  |  |

| 5        | PTD1      | 0      | P1 output "L"       |                     |  |  |  |

|          | 1101      | 1      | P1 output "H"       | Port data control   |  |  |  |

| 6        | PTD2      | 0      | P2 output "L"       | Port data control   |  |  |  |

|          | 1102      | 1      | P2 output "H"       |                     |  |  |  |

| 7        | PTD3      | 0      | P3 output "L"       |                     |  |  |  |

| ·<br>    | , ,,,,,   | 1      | P3 output "H"       |                     |  |  |  |

Note : The mark O around the status value means the reset status by the "L" level is input to  $\overline{AC}$  pin.

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### (2) Address F116

| DA  | Register  |        | Contents                                              |                                                                  |

|-----|-----------|--------|-------------------------------------------------------|------------------------------------------------------------------|

|     | ricgister | Status | Function                                              | Remarks                                                          |

| 0   | HP0       | 0      | If HS is the horizontal display start location.       | Horizontal display start location is                             |

| "   | (LSB)     | 1      | 5                                                     | specified using the 6 bits from HP5 to HP0.                      |

|     | LIDA      | 0      | $HS = T \times (4 \sum_{n=0}^{\infty} 2^n HP_n + N).$ | Note: HP5 to 0 = (000000)2 and (000001)2 settings are forbidden. |

| 1   | HP1       | 1      | T: The oscillation cycle of oscillator OSC1, OSC2     |                                                                  |

| 2   | HP2       | 0      |                                                       |                                                                  |

|     | 1112      | 1      |                                                       |                                                                  |

| 3   | 3 HP3 0   |        | HSZ11                                                 |                                                                  |

|     | ,,,,      | 1      | 0 0 9                                                 |                                                                  |

| 4   | HP4       | 0      | 0 1 10                                                |                                                                  |

| -   | 111 4     | 1      | 1 1 12                                                |                                                                  |

| 5   | HP5       | 0      |                                                       |                                                                  |

| Ŭ.  | (MSB)     | 1      |                                                       |                                                                  |

| 6   | PLTH      | 0      | Input polarity of HOR pin is negative.                | Set input polarity of HOD air                                    |

| , , | 1         | 1      | Input polarity of HOR pin is positive.                | Set input polarity of HOR pin.                                   |

| 7   | PLTV      | 0      | Input polarity of VERT pin is negative.               | Set input polarity of VERT pin.                                  |

|     |           | 1      | Input polarity of VERT pin is positive.               | Out input polarity of VEITI pill.                                |

Note: The mark O around the status value means the reset status by the "L" level is input to  $\overline{AC}$  pin.

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## (3) Address F216

| ĎΑ       | Register |        | Contents                                                                          | Remarks                                                                    |

|----------|----------|--------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| DA       | negister | Status | Function                                                                          | Henidika                                                                   |

| 0        | VP0      | 0      | If VS is the vertical display start location.                                     | The vertical start location is specified using the 6 bits from VP5 to VP0. |

| U        | (LSB)    | 1      | 5                                                                                 | asing the oblication. The to the co                                        |

| 1        | · VP1    | 0      | $VS = H \times (4 \sum_{n=0}^{\infty} 2^n VP_n + 3).$                             |                                                                            |

| <b>'</b> | VII      | 1      | H: Cycle with the horizontal synchronizing pulse                                  |                                                                            |

| 2        | VP2      | 0      | HOR                                                                               |                                                                            |

| 2        | 41.2     | 1      |                                                                                   |                                                                            |

| 3        | VP3      | 0      | lvs                                                                               |                                                                            |

|          |          | 1      |                                                                                   |                                                                            |

| 4        | VP4      | 0      | HS Character                                                                      |                                                                            |

| ,        |          | 1      | displaying area                                                                   |                                                                            |

| 5        | VP5      | 0      |                                                                                   |                                                                            |

|          | (MSB)    | 1      |                                                                                   |                                                                            |

| 6        | SEPV     | 0      | Input both horizontal synchronization signal and vertical synchronization signal. | The contents of synchronization signal input in superimpose display is al- |

|          |          | 1      | Input the horizontal (composite) synchronization signal only.                     | tered.                                                                     |

| 7        | INT/NON  | 0      | Interlace                                                                         | Scanning lines control (only in internal synchronization)                  |

| ,        |          | 1.     | Non-interlace                                                                     |                                                                            |

Note: The mark O around the status value means the reset status by the "L" level is input to  $\overline{AC}$  pin.

# M35017-XXXSP/FP

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### (4) Address F316

| DA | Register  |        | Contents                               |                                                                                 |

|----|-----------|--------|----------------------------------------|---------------------------------------------------------------------------------|

|    | rtegistei | Status | Function                               | - Remarks                                                                       |

| 0  | HSZ10     | 0      |                                        | Character size setting in the horizontal direction for the first line.          |

| 0  | H5210     | 1      | HSZ10 0 1                              | tal direction for the first line.                                               |

|    | HSZ11     | 0      | 0 1T/1dot 2T/1dot<br>1 3T/1dot 4T/1dot |                                                                                 |

| 1  | HSZII     | 1      | . 0171401 4177401                      |                                                                                 |

| 2  | HSZ20     | 0      |                                        | Character size setting in the horizon-                                          |

|    | H5220     | 1      | HSZ20 0 1                              | tal direction for the 2nd line to 10th line.                                    |

| 3  | HSZ21     | 0      | 0 1T/1dot 2T/1dot<br>1 3T/1dot 4T/1dot |                                                                                 |

| 3  | H3221     | 1      | 1 0                                    |                                                                                 |

| 4  | VSZ10     | 0      |                                        | Character size setting in the vertical direction for the first line.            |

| 4  | V3210     | 1      | VSZ10 0 1                              | direction for the mst line.                                                     |

| 5  | VSZ11     | 0      | 0 1H/1dot 2H/1dot<br>1 3H/1dot 4H/1dot |                                                                                 |

|    | VOZII     | 1      |                                        |                                                                                 |

| 6  | VSZ20     | 0      |                                        | Character size setting in the vertical direction for the 2nd line to 10th line. |

|    | V 3220    | 1      | VSZ20 0 1                              | direction for the 210 line to 10th line.                                        |

| 7  | VSZ21     | 0      | 0 1H/1dot 2H/1dot<br>1 3H/1dot 4H/1dot |                                                                                 |

| ,  | 10221     | 1      |                                        |                                                                                 |

Note : The mark O around the status value means the reset status by the "L" level is input to  $\overline{AC}$  pin.

# M35017-XXXSP/FP

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### (5) Address F416

|      | Devistan |                                                             | Contents                                                  |                                                 |                                           | Rema               | arko                                  |  |  |  |

|------|----------|-------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------|-------------------------------------------|--------------------|---------------------------------------|--|--|--|

| DA . | Register | Status                                                      | Function                                                  |                                                 |                                           | nem                | ains .                                |  |  |  |

|      | DSP0     | 0                                                           | Line 1 is in the display mode specified by BLK0 and BLK1. |                                                 | to DS                                     |                    | each controlled in-                   |  |  |  |

| 0    | DSPU     | 1                                                           | Line 1 is in a different display mode.                    | <u>  _                                     </u> | BLKO                                      | $\overline{}$      | Display mode                          |  |  |  |

|      | D0D4     | 0                                                           | Line 2 is in the display mode specified by BLK0 and BLK1. |                                                 |                                           | 0                  | for line n  Border (Note 1)           |  |  |  |

| 1    | DSP1     | 1                                                           | Line 2 is in a different display mode.                    | ]                                               | 0                                         | 1                  | Character                             |  |  |  |

|      |          | 0                                                           | Line 3 is in the display mode specified by BLK0 and BLK1. | 0                                               | 1                                         | 0                  | Character                             |  |  |  |

| 2    | DSP2     | 1                                                           | Line 3 is in a different display mode.                    | ٦١_                                             | ļ .                                       | 1                  | Border                                |  |  |  |

|      |          | 0                                                           | Line 4 is in the display mode specified by BLK0 and BLK1. | 1                                               | 0                                         | 0                  | Border Matrix-outline                 |  |  |  |

| 3    | DSP3     | 1                                                           | Line 4 is in a different display mode.                    | ┨├                                              |                                           | 0                  | Matrix-outline                        |  |  |  |

|      |          | 0                                                           | Line 5 is in the display mode specified by BLK0 and BLK1. | -   1                                           | 1                                         | 1                  | Character                             |  |  |  |

| 4    | DSP4     | 1                                                           | Line 5 is in a different display mode.                    |                                                 | DSPn in the generic name for DSP0 to DSP9 |                    |                                       |  |  |  |

|      | Done     | 0                                                           | Line 6 is in the display mode specified by BLK0 and BLK1. |                                                 |                                           |                    | y mode for line n is                  |  |  |  |

| 5    | DSP5     | 1                                                           | Line 6 is in a different display mode.                    | lines                                           | , the di                                  | size, a<br>splay m | and for the other ode is the charac-  |  |  |  |

|      | Done     | 0                                                           | Line 7 is in the display mode specified by BLK0 and BLK1. |                                                 | DSPn (                                    |                    | 9) are "0", the dis-<br>blanking OFF. |  |  |  |

| 6    | DSP6     | 1                                                           | Line 7 is in a different display mode.                    | Note                                            | 2: D                                      |                    | nd DSP9 are as-                       |  |  |  |

| 7    | DSP7     | ① Line 8 is in the display mode specified by BLK0 and BLK1. |                                                           | Signe                                           | o io ai                                   | 101000 F           | 010.                                  |  |  |  |

| 7    | USP/     | 1                                                           | Line 8 is in a different display mode.                    |                                                 |                                           |                    |                                       |  |  |  |

Note : The mark O around the status value means the reset status by the "L" level is input to  $\overline{AC}$  pin.

# M35017-XXXSP/FP

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### (6) Address F516

| DA | Register  |        | Contents                                                                         | Remarks                                                                                                              |

|----|-----------|--------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|    | riegistei | Status | Function                                                                         | heiliarks                                                                                                            |

|    | DSP8      | 0      | Line 9 is in the display mode specified by BLK0 and BLK1.                        | See the remarks of DSP0 to DSP7                                                                                      |

| 0  | DOPO      | 1      | Line 9 is in the different display mode.                                         | (address F416).                                                                                                      |

|    | 5050      | 0      | Line 10 is in the display mode specified by BLK0 and BLK1.                       |                                                                                                                      |

| 1  | DSP9      | 1      | Line 10 is in the different display mode.                                        |                                                                                                                      |

|    |           | 0      |                                                                                  | These registers are used to extend                                                                                   |

| 2  | EXP0      | 1      | EXP0 0 1  Normal character Reversed character                                    | the function of the EXP bits in the addresses 016 to EF16 of the display RAM.  Blinking function do not operate when |

| 3  | EXP1      | 0      | O Blinking (No blinking) Normal character Reversed character Exclusion Exclusion | register is a reversed character.                                                                                    |

|    |           | 1      | Exclusion Exclusion                                                              |                                                                                                                      |

|    | TEST0     | 0      | TEST0 to TEST2 = (000)2 → Normal display                                         |                                                                                                                      |

| 4  | 15510     | 1      | = (010)2 → Space display                                                         |                                                                                                                      |

| 5  | TEST1     | 0      |                                                                                  |                                                                                                                      |

| 5  | 15911     | 1      |                                                                                  |                                                                                                                      |

| 6  | TEST2     | 0      |                                                                                  |                                                                                                                      |

| Ů  | 15312     | 1      |                                                                                  |                                                                                                                      |

| 7  |           | 0      | M-PAL 0 1                                                                        | Synchronization signal is selected with this register and MPAL register                                              |

|    | 14/17     | 1      | 0         NTSC         M-PAL           1         PAL         Do not use          | (address F616).                                                                                                      |

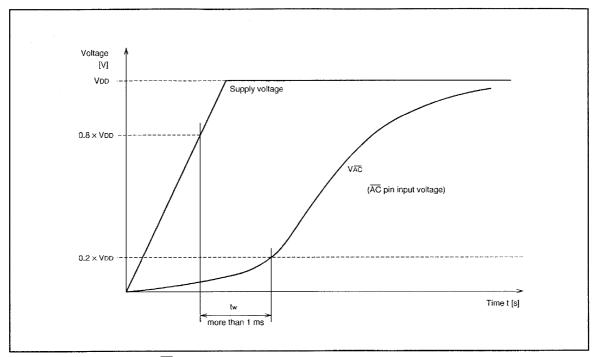

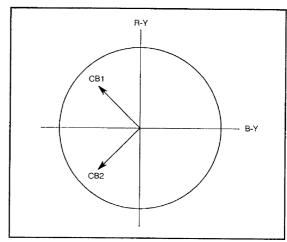

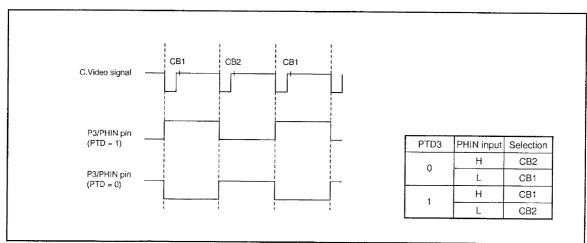

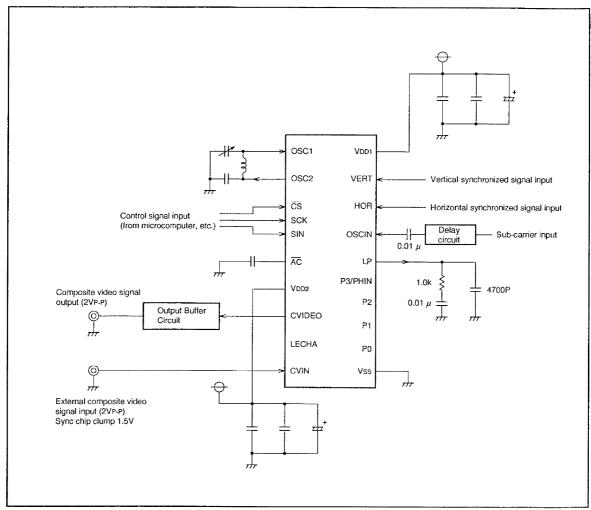

Note: The mark O around the status value means the reset status by the "L" level is input to  $\overline{AC}$  pin.